|

在半導體產業的精密賽道上���,每一顆芯片的誕生��,都離不開無數環節的微米級精準把控。當5nm製程成為行業主流���,當Chiplet�、3D堆疊等新工藝不斷突破傳統邊界��,芯片製造對治具的精度��、適(shi)配(pei)性(xing)與(yu)穩(wen)定(ding)性(xing)提(ti)出(chu)了(le)嚴(yan)苛(ke)要(yao)求(qiu)。東(dong)莞(guan)路(lu)登(deng)科(ke)技(ji)�,憑(ping)借(jie)深(shen)耕(geng)半(ban)導(dao)體(ti)領(ling)域(yu)的(de)技(ji)術(shu)沉(chen)澱(dian)�����,推(tui)出(chu)新(xin)一(yi)代(dai)半(ban)導(dao)體(ti)晶(jing)圓(yuan)機(ji)器(qi)人(ren)治(zhi)具(ju)��,以(yi)三(san)大(da)核(he)心(xin)技(ji)術(shu)重(zhong)構(gou)製(zhi)造(zao)標(biao)準(zhun)�,為(wei)全(quan)球(qiu)芯(xin)片(pian)企(qi)業(ye)打(da)造(zao)從(cong)切(qie)割(ge)到(dao)封(feng)裝(zhuang)的(de)全(quan)場(chang)景(jing)精(jing)密(mi)解(jie)決(jue)方(fang)案(an)。

微米級精度�����,築牢良率護城河。路登治具搭載智能溫控補償係統���,采用航天級鈹銅合金基材����,配合納米級熱膨脹係數算法��,在-40℃至150℃的極端環境下��,形變量控製在0.01%以內���,徹底解決傳統治具因溫度漂移導致的對位偏差問題。內置的128個壓力傳感器組成AI自診斷網絡�,實時監測晶圓受力分布�,一旦檢測到異常應力��,立即觸發三級預警機製��,將芯片崩邊率降至0.003‰。某頭部IDM企業導入後��,12英寸晶圓良率從92.1%躍升至98.7%����,年返工成本直接縮減超2000萬元。

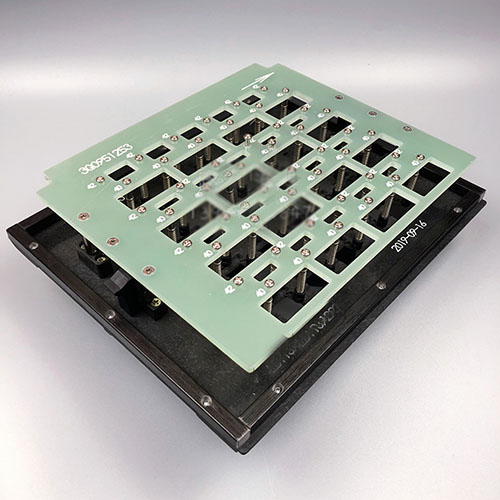

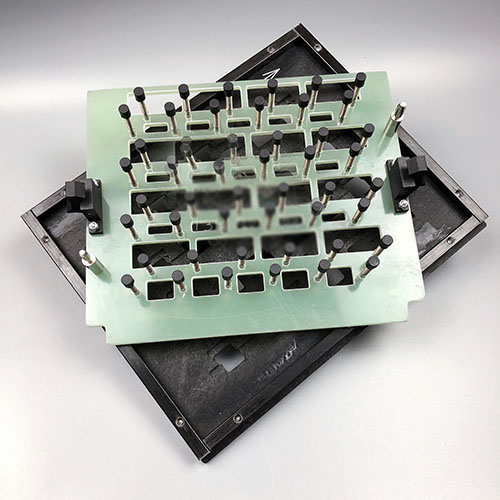

全(quan)場(chang)景(jing)適(shi)配(pei)��,賦(fu)能(neng)工(gong)藝(yi)革(ge)新(xin)。麵(mian)對(dui)芯(xin)片(pian)封(feng)裝(zhuang)形(xing)態(tai)的(de)多(duo)元(yuan)化(hua)趨(qu)勢(shi)�����,路(lu)登(deng)治(zhi)具(ju)采(cai)用(yong)多(duo)模(mo)態(tai)吸(xi)附(fu)技(ji)術(shu)���,通(tong)過(guo)微(wei)孔(kong)陣(zhen)列(lie)真(zhen)空(kong)電(dian)磁(ci)雙(shuang)模(mo)鎖(suo)定(ding)方(fang)案(an)��,可(ke)無(wu)縫(feng)適(shi)配(pei)8英寸晶圓�����、QFN封裝等12種芯片形態�����,切換時間僅需3秒�,效率較傳統夾具提升400%。在倒裝焊環節��,0.1mm超薄基板支持3D堆疊芯片的精準對位��;老化測試階段�����,耐腐蝕陶瓷鍍層通過168小時鹽霧試驗����,輕鬆滿足車規級認證要求。國內某先進封裝企業憑借其模塊化設計����,將產線改造周期從2周壓縮至3天�����,快速響應了Chiplet新工藝的量產需求。

降(jiang)本(ben)增(zeng)效(xiao)����,重(zhong)構(gou)產(chan)業(ye)價(jia)值(zhi)。路(lu)登(deng)治(zhi)具(ju)不(bu)僅(jin)在(zai)精(jing)度(du)與(yu)適(shi)配(pei)性(xing)上(shang)領(ling)先(xian)行(xing)業(ye)����,更(geng)從(cong)細(xi)節(jie)處(chu)為(wei)客(ke)戶(hu)創(chuang)造(zao)成(cheng)本(ben)價(jia)值(zhi)。切(qie)割(ge)環(huan)節(jie)的(de)金(jin)剛(gang)石(shi)塗(tu)層(ceng)邊(bian)緣(yuan)設(she)計(ji)��,減(jian)少(shao)晶(jing)圓(yuan)崩(beng)邊(bian)的(de)同(tong)時(shi)����,使(shi)刀(dao)片(pian)壽(shou)命(ming)延(yan)長(chang)30%�����;磁吸式Socket結構支持秒級模組更換��,兼容COB��、COG等多種封裝工藝��,幫助某頭部企業將產能提升3倍以上�,人力成本降低超40%。從Mini LED背光的0.05mm超薄芯片貼裝�,到Micro LED巨量轉移的2000+芯片單次承載��,路登治具以全場景解決方案����,為半導體產業的高質量發展注入強勁動力

|